# Hybrid Reactive Power Compensators and Firefly Algorithm Based Optimal PI Controller for a Multi-terminal HVDC Transmission System Feeding Weak AC Networks

S. Seenivasan<sup>#1</sup>and S. Singaravelu<sup>\*2</sup>

\*Assistant Professor, \*Professor, Department of Electrical Engineering, Annamalai University, Annamalainagar-608002, Tamil Nadu, India.

#### **Abstract**

This paper presents a line commutated converter (LCC) based multi-terminal HVDC (MTDC) transmission system feeding weak AC networks with hybrid reactive power compensators (RPC's) at the inverters AC side. The hybrid compensator is achieved by an equal mixture of any two of the following compensators: synchronous compensator (SC); static var compensator (SVC); static synchronous compensator (STATCOM). The HVDC transmission system model is executed in the Matlab environment with the firefly algorithm based optimal proportional integral (PI) controller for rectifiers and inverters The transient performances of hybrid RPC's (SC+SVC, SVC+STATCOM and SC+STATCOM) are evaluated under various fault conditions and the outcomes are compared with the performance of the SC, SVC and STATCOM to focus the supremacy of the hybrid compensators. The simulation results certify that the equal mix of SC and STATCOM has a steady and fastest response. The results also demonstrate the supremacy of the firefly algorithm based optimal PI controller over the conventional PI controller. The harmonic analysis is also done under steady state operation to assure the quality of power supply on the inverters AC side.

**Keywords:** Firefly algorithm, Hybrid RPC's, MTDC, PI controller, Weak AC network.

# 1. Introduction

The MTDC power transmission technology has 1) rapid rises in the power carrying capacity, 2) flexibility in power control and 3) possibility of connecting new offshore load/generation terminal. During occurrence of the fault, in the MTDC system without appropriate control and protection, the fault at one terminal will affect the

interconnected terminals [1], [2]. Under such circumstances of the MTDC system, by presuming that the blocking of the converter is successful, special control and protection is offered. On the other hand, this presumption is not necessarily valid in terms of the practical operation of converters in the HVDC system such as 1) During the communication outage of control signals, the whole converter can be out of control and cannot be blocked, 2) A more common condition is that one of the six pulse converter arm is failed to be blocked [3-5]. Hence, it is worth identifying the possible hazard to the MTDC system by propagating the fault at one terminal without blocking the converters.

Further, the behavior of the HVDC system plays ever greater roles in the performance of entire AC/DC power systems. It is necessary to understand the mechanisms of the interactions between an HVDC system and an AC network so the HVDC system can be operated in a manner that enhances the stability of the entire power grid. The impact of this interaction largely depends on the strength of the AC system at the converter bus [6], which is generally expressed by the short circuit ratio (SCR). The following SCR values [7] can be used to classify AC systems: a) For a strong system SCR > 3, b) For a weak system SCR < 3, c) For a very weak system SCR < 3.

Enormous amount of work has been carried out so far to know the interaction between AC network and HVDC system. The voltage stability associated phenomena [8] at monopolar HVDC terminals feeding weak AC network and solutions for eradicating the risks of voltage collapse and for evading control-induced oscillations was discussed. An analysis of the Nelson River monopolar HVDC system with new synchronous compensators [9] is presented and also highlighted planning requirements and specification of the synchronous compensators to optimize power delivery by the DC links. The dynamic performance of monopolar HVDC systems [10] connected to a weak AC system is analyzed for various exciter characteristics of synchronous machines connected to the converter bus. The direct transient stability margin (TSM) prediction method using the extended equal area criterion [11] is used for the incorporation of SVC and monopolar HVDC transmission system into the power system. The use of STATCOM at the inverter end of a conventional monopolar HVDC system for the reactive power support is discussed in [12]. An evaluation of the coordination between STATCOM and monopolar HVDC classic link feeding a weak AC network is done in [13] with two different control technique during various fault conditions.

The fault recovery and suppression of dynamic overvoltage (DOV) criterion of a monopolar HVDC system feeding a weak AC network have been discussed in [14] with a fixed capacitor (FC), SC, thyristor controlled reactor (TCR), thyristor switched capacitor (TSC), metal oxide varistor (MOV), series capacitor device (SCD). The DC power recovery and suppression of temporary overvoltage (TOV) of a monopolar HVDC system feeding a very weak AC network have been discussed in [15], [16]. In order to make the analysis complete, it is highly necessary to consider the suppression of TOV and fault recovery of a monopolar HVDC system feeding a weak AC network. Therefore, in [17] simulation of both the fault recovery performance as well as suppression of TOV during various transient fault conditions has been carried out for a monopolar HVDC system connected to a weak AC network with the hybrid

RPC's: SC+SVC, SC+STATCOM and SVC+STATCOM. As an addition, in this paper, the detailed simulation study carried out in a monopolar HVDC system is extended to a multi-terminal HVDC system by analyzing the DC power recovery performance and suppression of TOV during various transient fault conditions. The harmonic investigation is also carried out under steady state to assure the quality of power supply on inverter AC sides.

The simple fixed gain PI controller used for the rectifier and the inverter controllers of HVDC system causes instability due to inadequacy in tuning its gain for various abnormal operating conditions. To overcome this drawback intelligent technique has been introduced [18-21] for proper tuning of the PI controller parameters. However, in all those tuning methods the principal signals used to fix the PI gains of the rectifier and the inverter current controllers are current error and its derivative. On the other hand, for the inverter gamma controller, the gamma error and its derivative are used. In this paper, minimization of the rectifier and the inverter DC power errors are considered as an objective function which is achieved by the firefly optimization algorithm, to fix the PI gains of the respective PI controller. To determine the effectiveness of the firefly algorithm based optimal PI controller on transient performance of HVDC system, it has been compared with conventional PI controller.

# 2. Modelling of Monopolar HVDC Transmission System

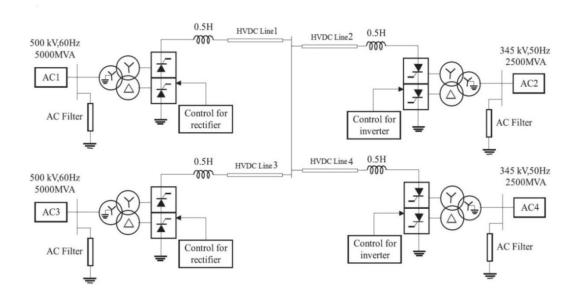

A line commutated converter based four-terminal HVDC system feeding two strong AC networks is presented in [22], in which inverter side AC networks are replaced by weak AC networks as shown in the Fig. 1.

Fig. 1: Four-Terminal HVDC transmission system model feeding weak AC networks.

Each rectifier side AC system of 500kV, 5000MVA, 60Hz is connected to each inverter side AC system of 345kV, 2500MVA, 50Hz through an HVDC network.

Generally, the AC system is represented by damped LLR equivalents. The Passive filters of 450MVAr are connected on the source side to eliminate the 11th and 13th (the double tuned type) order and above 24th (second order high pass filter) order current harmonics and synchronous or static compensator or fixed capacitor with synchronous or static compensator is used (150MVAr) for reactive power compensation. Each rectifier and inverter is 12-pulse converters. The DC network model consists of a smoothing reactor for the rectifier and the inverter bridges, a passive filter of double tuned type to mitigate the 12th and 24th order DC voltage harmonics and the DC line. The DC link of 1500 km is modelled as a distributed parameter line model with lumped losses. Each rectifier is equipped with a current controller to maintain the DC system current constant. Each inverter is provided with a current controller to maintain the DC system current constant and a constant The reference current for the current extinction angle or gamma controller. controllers is obtained from the master controller output through the voltage dependent current order limiter (VDCOL). In order to protect each rectifier and each inverter DC protection functions are implemented in each converter.

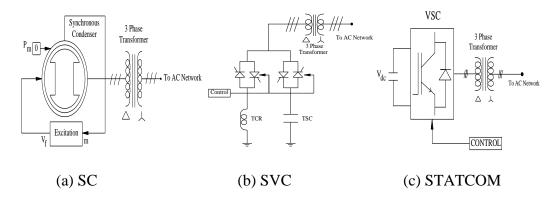

Fig. 2: Schematic of RPC's

In the inverter side AC network, the following six reactive power compensator options is studied.

### 2.1 SC

The SC model of 150MVAr shown in Fig. 2 (a) is represented with the simplified synchronous machine block which models, both the electrical and mechanical characteristics of a simple synchronous machine. The SC uses the solid static excitation system.

### 2.2 SVC

A 150MVAr SVC is shown in Fig. 2 (b) regulates voltage on a 345kV system. The SVC consists of a 345kV/16kV, 168MVA coupling transformer, one 60MVAr TCR bank and one 180MVAr TSC connected to the secondary side of the transformer. Switching the TSC in and out allows a continuous variation of the secondary reactive

power from zero to 180MVAr capacitive, whereas phase control of the TCR allows a continuous variation from zero to 60MVAr inductive.

### 2.3 STATCOM

The STATCOM) shown in Fig. 2 (c) is located at the inverter side of the HVDC link and has a rating of  $\pm 150$ MVAr. This STATCOM is a typical simple PWM voltage source converter (VSC). It consists of a 6 pulse VSC inverter and a series connected Capacitors which act as a variable DC voltage source. Based on a VSC, the STATCOM regulates system voltage by absorbing or generating reactive power.

### 2.4 An Equal Mix of SC and SVC

The SC and SVC (-90MVAr, +30MVAr) are connected to the inverter bus in this scheme with the rating of the SC halved to 75Mvar. In steady state the SC and SVC each supply 75MVAr.

# 2.5 An Equal Mix of SC and STATCOM

The SC and STATCOM (±75MVAr) are connected to the inverter bus in this scheme with the rating of the SC halved to 75Mvar. In steady state the SC and STATCOM each supply 75MVAr.

# 2.6 An Equal Mix of SVC and STATCOM

The SVC (-90MVAr, +30MVAr) and STATCOM (±75MVAr) are connected to the inverter bus in this scheme. In steady state the SVC and STATCOM each supply 75MVAr.

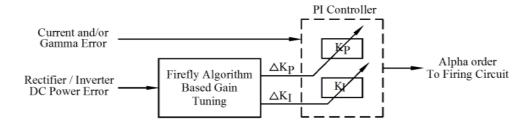

# 3. Application of Firefly Algorithm for Obtaining Optimal Gain Values for PI Controllers

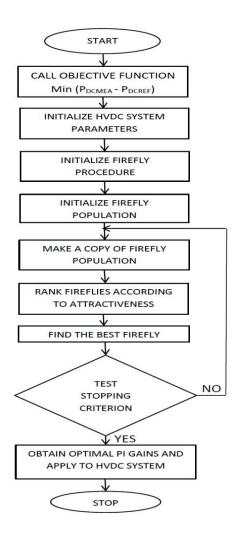

In this paper, optimization of the rectifier and the inverter side DC power error is picked as a prime objective function which has to be minimized. To achieve the same DC power ( $P_{DCMEA}$ ) and its reference ( $P_{DCREF}$ ) is compared to get the error signal. The integral square error of the rectifier DC power error and inverter DC power error are processed by the firefly algorithm [23-25] to fix the gain of the rectifier current PI controller and to fix the gain of the both inverter current PI controller and the gamma PI controller respectively.

**Fig. 3:** Schematic diagram of the firefly algorithm based tuning technique.

**Fig. 4:** Flowchart for minimization of the rectifier/the inverter DC power error function using firefly algorithm.

This approach ensures the reduced computational procedure, faster recovery and reduced TOV. The schematic diagram of the firefly algorithm based tuning technique is shown in Fig. 3. The general flow chart for minimization of the rectifier/ the inverter DC power error function using firefly algorithm is shown in Fig. 4.

# 4. Simulation Results and Discussion

In order to know the interaction between AC network and HVDC systems, MATLAB simulation model is implemented based on the data [26]. At the inverter AC side the following RPC's are considered for analysis: SC, SVC, STATCOM, SC+SVC, SC+STATCOM and SVC+STATCOM. In all the cases simulated steady state AC voltage and current waveforms at the inverter AC side and their harmonic spectrums are observed to assure the quality of the AC supply.

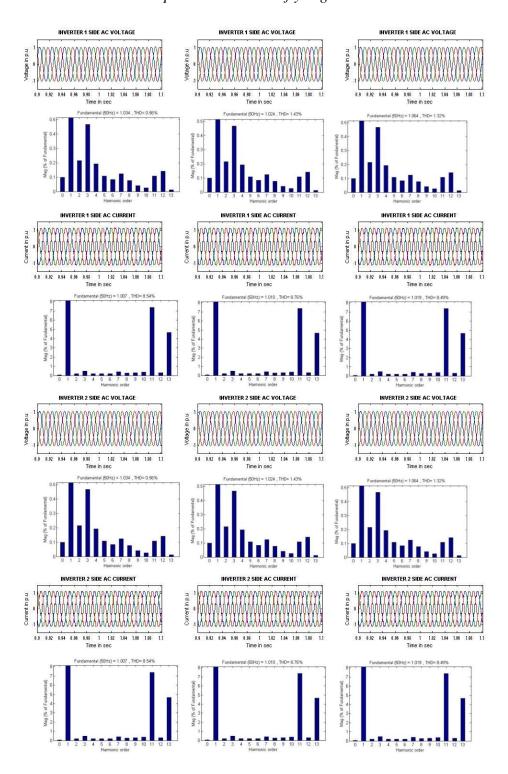

**Fig. 5:** Inverter 1 and 2 sides AC waveforms and their harmonic spectrums during steady state operation -with SC (left), -with SVC (middle), -with STATCOM (right).

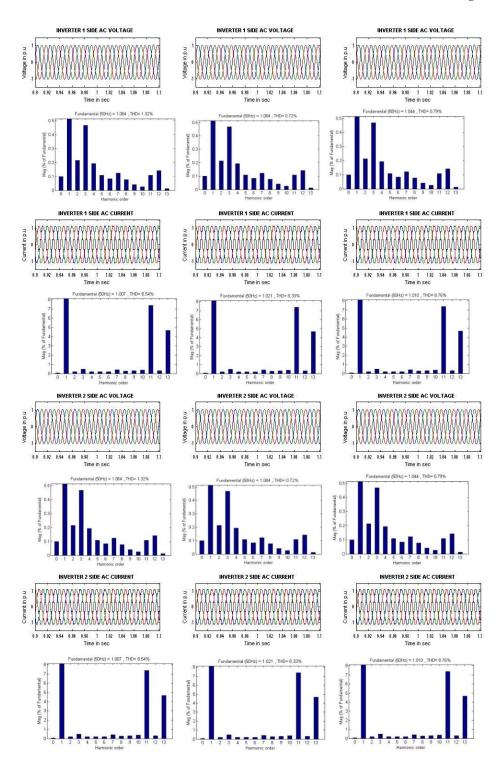

**Fig. 6:** Inverter 1 and 2 sides AC waveforms and their harmonic spectrums during steady state operation -with SC+SVC (Left), -with SC+STATCOM (Middle), -with SVC+STATCOM (Right).

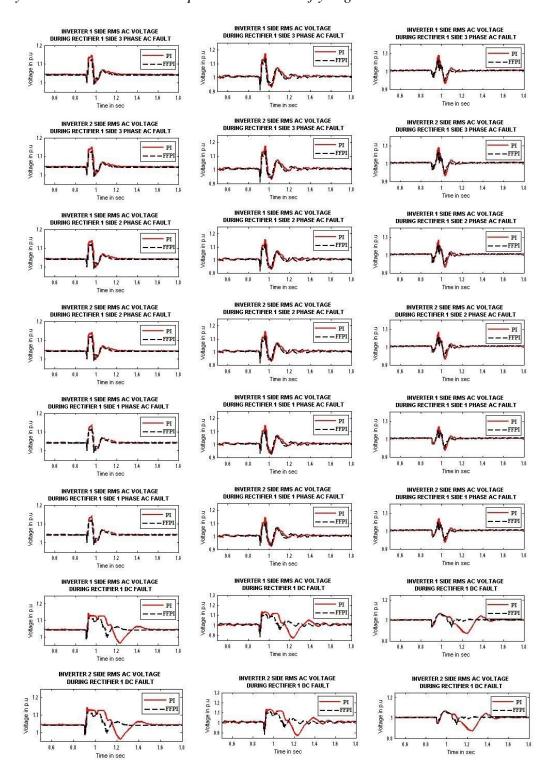

**Fig. 7:** Inverter 1 and 2 AC bus RMS voltage when disturbances occur on the DC line or at the rectifier AC side -with SC (left), -with SVC (middle), -with STATCOM (right).

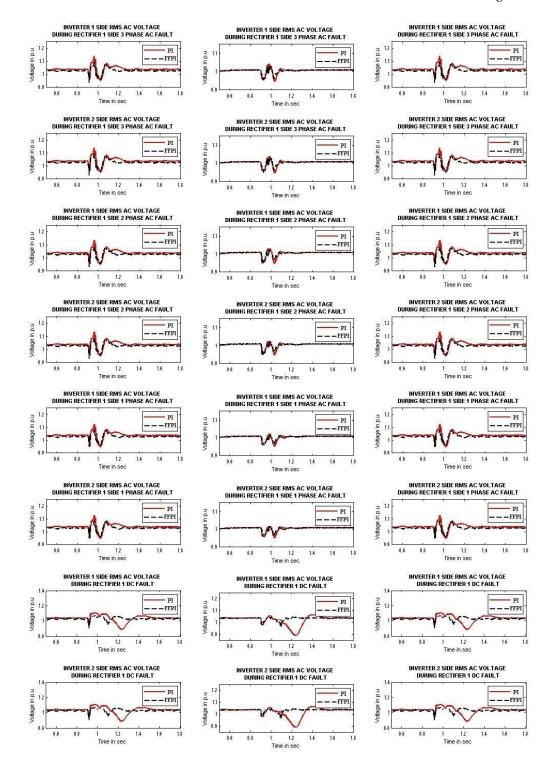

**Fig. 8:** Inverter 1 and 2 AC bus RMS voltage when disturbances occur on the DC line or at the rectifier AC side -with SC+ SVC (Left), -with SC+STATCOM (Middle), -with SVC+STATCOM (Right).

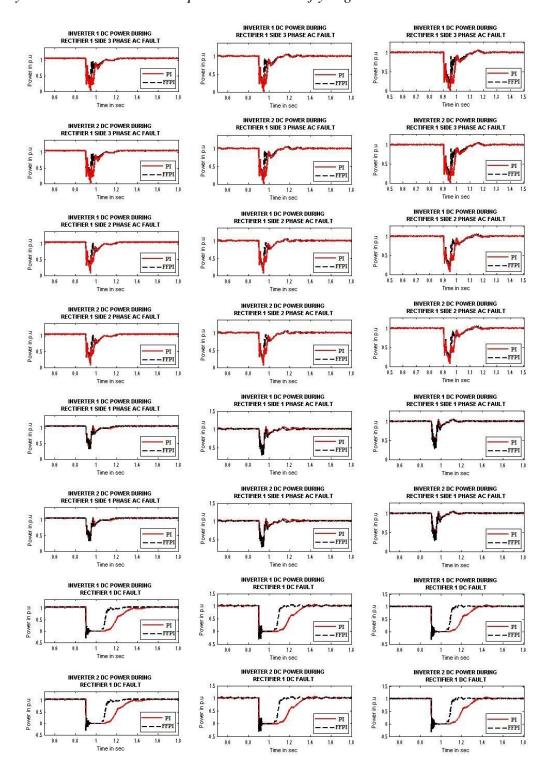

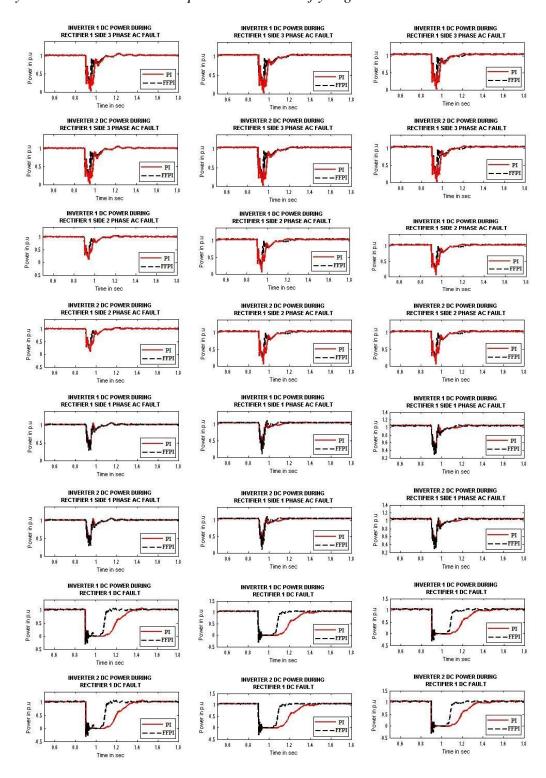

**Fig. 9:** Inverter 1 and 2 DC power when AC and DC disturbances occur on the rectifier 1 side -with SC (Left), -with SVC (Middle), -with STATCOM (Right).

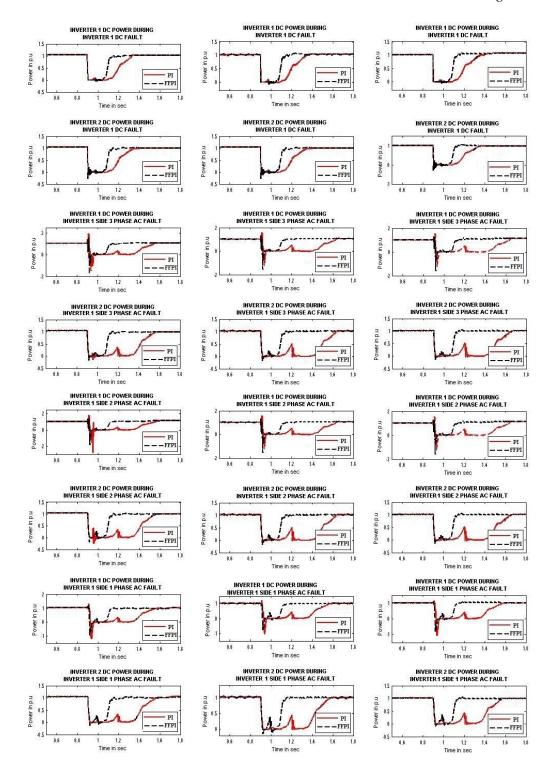

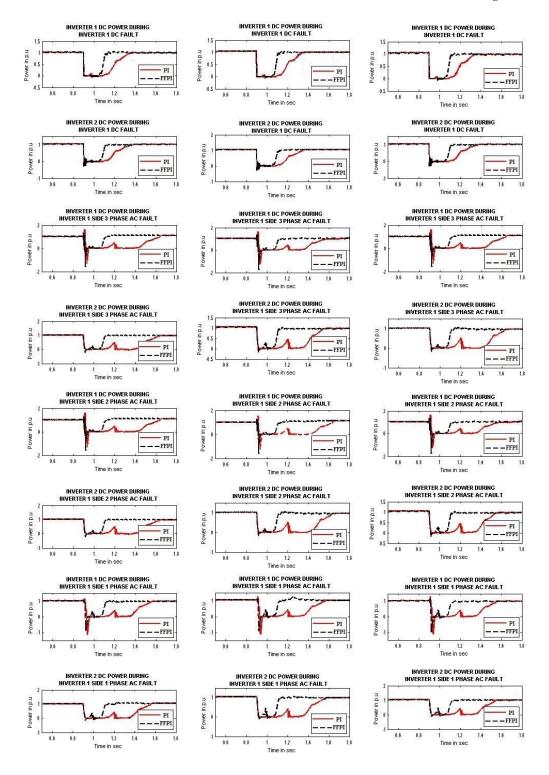

**Fig. 10:** Inverter 1 and 2 DC power when AC and DC disturbances occur on the inverter 1 side -with SC (Left), -with SVC (Middle), -with STATCOM (Right).

**Fig. 11:** Inverter 1 and 2 DC power when AC and DC disturbances occur on the rectifier 1 side -with SC+SVC (Left), -with SC+STATCOM (Middle), -with SVC+STATCOM (Right).

**Fig. 12:** Inverter 1 and 2 DC power when AC and DC disturbances occur on the inverter 1 side -with SC+SVC (Left), -with SC+STATCOM (Middle), -with SVC+STATCOM (Right).

**Table I:** Harmonics present in the inverter side AC quantities with SC, SVC and STATCOM

| % AC Harmonics for various RPC's |                   | SC   | SVC  | STATCOM |

|----------------------------------|-------------------|------|------|---------|

| Voltage                          | Inverter 1        | 0.56 | 1.43 | 1.32    |

|                                  | <b>Inverter 2</b> | 0.56 | 1.43 | 1.32    |

| Commont                          | Inverter 1        | 8.54 | 8.76 | 8.49    |

| Current                          | <b>Inverter 2</b> | 8.54 | 8.76 | 8.49    |

Table II: Harmonics present in the inverter side AC quantities with Hybrid RPCs

| % AC Harmonicsfor various RPC's |            | SC+SVC | SC+<br>STATCOM | SVC+<br>STATCOM |

|---------------------------------|------------|--------|----------------|-----------------|

| Voltage                         | Inverter 1 | 1.32   | 0.72           | 0.79            |

|                                 | Inverter 2 | 1.32   | 0.72           | 0.79            |

| Current                         | Inverter 1 | 8.54   | 8.33           | 8.76            |

|                                 | Inverter 2 | 8.54   | 8.33           | 8.76            |

**Table III:** Level of Over voltage when disturbances occur on the DC line or at the rectifier 1 side during DC block.

| TOV for various RPC's in p.u |      |            | side 3Φ AC<br>ult |            | side 2Ф AC<br>ult |

|------------------------------|------|------------|-------------------|------------|-------------------|

|                              |      | Inverter 1 | Inverter 2        | Inverter 1 | Inverter 2        |

| SC                           | PI   | 1.1668     | 1.1668            | 1.1432     | 1.1432            |

| SC                           | FFPI | 1.1349     | 1.1349            | 1.1172     | 1.1172            |

| SVC                          | PI   | 1.1712     | 1.1712            | 1.1502     | 1.1502            |

| SVC                          | FFPI | 1.1405     | 1.1405            | 1.1229     | 1.1229            |

| STATCOM                      | PI   | 1.0711     | 1.0711            | 1.0681     | 1.0681            |

| STATCOM                      | FFPI | 1.0449     | 1.0449            | 1.0421     | 1.0421            |

| SC+SVC                       | PI   | 1.1277     | 1.1277            | 1.1045     | 1.1045            |

| SC+SVC                       | FFPI | 1.0986     | 1.0986            | 1.0778     | 1.0778            |

| SC+                          | PI   | 1.0296     | 1.0296            | 1.0143     | 1.0143            |

| STATCOM FFP:                 | FFPI | 1.0025     | 1.0025            | 1.0029     | 1.0029            |

| SVC+                         | PI   | 1.1168     | 1.1168            | 1.0984     | 1.0984            |

| STATCOM                      | FFPI | 1.0885     | 1.0885            | 1.0682     | 1.0682            |

The transient performance of the HVDC system is analyzed in the presence of various RPC'S for a duration of two seconds under different fault conditions to study the suppression of TOV and fault recovery. For the purposes of comparison, identical fault duration of 0.05seconds was used for all types of faults. During the transient performance analysis the following cases are considered: (1) Fault at rectifier station 1 and their impact on inverter station 1 and 2, (2) Fault at inverter station 1 and their

impact on inverter station 1 and 2. Since the rectifier 1 and 2 and inverter 1 and 2 are identical in the system under study discussion is limited to the cases mentioned above. The inverter side RMS AC voltage waveforms are observed during various AC faults and DC fault on the rectifier side to study the TOV suppression capability of the proposed firefly algorithm based PI controller. For analyzing the fault recovery capability with the proposed firefly algorithm based PI controller, the inverter DC power is observed, under various AC faults and DC faults at rectifier and inverter side. In all the cases, the TOV suppression and fault clearance capability of the firefly algorithm based PI controller are compared with conventional PI controller of an HVDC transmission system.

### 4.1 Inverter Side AC Harmonics

The inverter side AC voltage and current waveforms and their harmonic spectrums during steady state operation are shown in Fig. 5, 6 and the results are listed in table I, II. From the inverter side AC waveforms and their harmonic spectrum, it is found that in all the cases the voltage and current are equal to 1p.u and the harmonics are within tolerable limit. The 11<sup>th</sup> and 13<sup>th</sup> current harmonics are the foremost harmonics on the inverters AC side.

**Table IV:** Level of Over voltage when disturbances occur on the DC line or at the rectifier 1 side during DC block.

| TOV for various<br>RPC's in p.u |        | Rectifier<br>AC | 1 side 1Φ<br>fault | Rectifier 1 DC faul |            |

|---------------------------------|--------|-----------------|--------------------|---------------------|------------|

|                                 |        | Inverter 1      | Inverter 2         | Inverter 1          | Inverter 2 |

| SC                              | PI     | 1.1285          | 1.1285             | 1.1289              | 1.1289     |

| SC                              | FFPI   | 1.0974          | 1.0974             | 1.1045              | 1.1045     |

| SVC                             | PI     | 1.1395          | 1.1395             | 1.1363              | 1.1363     |

| SVC                             | FFPI   | 1.1075          | 1.1075             | 1.1101              | 1.1101     |

| CTATCOM                         | PI     | 1.0494          | 1.0494             | 1.0715              | 1.0715     |

| STATCOM                         | FFPI   | 1.0214          | 1.0214             | 1.0445              | 1.0445     |

| SC+SVC                          | PI     | 1.0882          | 1.0882             | 1.0879              | 1.0879     |

| SC+SVC                          | FFPI   | 1.0592          | 1.0592             | 1.0597              | 1.0597     |

| SC+                             | PI     | 1.0039          | 1.0039             | 1.0249              | 1.0249     |

| STATCOM FFPI                    | 1.0026 | 1.0026          | 1.0084             | 1.0084              |            |

| SVC+                            | PI     | 1.0672          | 1.0672             | 1.0776              | 1.0776     |

| STATCOM                         | FFPI   | 1.0390          | 1.0390             | 1.0509              | 1.0509     |

# 4.2 Temporary overvoltage

When disturbances occur on the DC line or at the rectifier side, commonly temporary over voltage happens. It is usual practice a large number RLC based filters are provided in the inverter side of the HVDC system, in order to supply the part of necessary reactive power. During rectifier side AC or DC faults (the inverter side has no faults), the DC is blocked, and hence the reactive power of those filters will flow

into the AC system, which often causes TOV. In order to suppress the TOV, the reactive power compensator and DC system PI controllers should respond quickly otherwise the TOV could be very high and could damage the insulation of the equipment. The ability of TOV suppression of various RPC's is demonstrated with the proposed firefly algorithm based PI controller and also compared to a conventional PI controller.

**Table V:** Inverter 1 and 2 DC power recovery time during AC and DC disturbances occur on the rectifier 1 side.

| DC power recovery time for various |      |            |            |            | ïer 1 side 2Ф<br>AC fault |  |

|------------------------------------|------|------------|------------|------------|---------------------------|--|

| RPC's in seconds                   |      | Inverter 1 | Inverter 2 | Inverter 1 | Inverter 2                |  |

| SC                                 | PI   | 0.085      | 0.085      | 0.074      | 0.074                     |  |

| SC                                 | FFPI | 0.041      | 0.041      | 0.034      | 0.034                     |  |

| SVC                                | PI   | 0.095      | 0.095      | 0.080      | 0.080                     |  |

| SVC                                | FFPI | 0.046      | 0.046      | 0.039      | 0.039                     |  |

| STATCOM                            | PI   | 0.080      | 0.080      | 0.070      | 0.070                     |  |

| STATCOM                            | FFPI | 0.036      | 0.036      | 0.029      | 0.029                     |  |

| SC+                                | PI   | 0.079      | 0.079      | 0.068      | 0.068                     |  |

| SVC                                | FFPI | 0.035      | 0.035      | 0.030      | 0.030                     |  |

| SC+                                | PI   | 0.069      | 0.069      | 0.058      | 0.058                     |  |

| STATCOM                            | FFPI | 0.022      | 0.022      | 0.018      | 0.018                     |  |

| SVC+                               | PI   | 0.078      | 0.078      | 0.067      | 0.067                     |  |

| STATCOM                            | FFPI | 0.034      | 0.034      | 0.029      | 0.029                     |  |

**Table VI:** Inverter 1 and 2 DC power recovery time during AC and DC disturbances occur on the rectifier 1 side.

| DC power recovery time for various |      |            | side 1Ф AC<br>ult | Rectifier 1 DC f |            |

|------------------------------------|------|------------|-------------------|------------------|------------|

| RPC's in seconds                   |      | Inverter 1 | Inverter 2        | Inverter 1       | Inverter 2 |

| SC                                 | PI   | 0.048      | 0.048             | 0.344            | 0.344      |

| SC                                 | FFPI | 0.019      | 0.019             | 0.162            | 0.162      |

| SVC                                | PI   | 0.055      | 0.055             | 0.356            | 0.356      |

| SVC                                | FFPI | 0.024      | 0.024             | 0.168            | 0.168      |

| STATCOM                            | PI   | 0.043      | 0.043             | 0.332            | 0.332      |

| STATCOM                            | FFPI | 0.016      | 0.016             | 0.154            | 0.154      |

| SC+                                | PI   | 0.038      | 0.038             | 0.329            | 0.329      |

| SVC                                | FFPI | 0.012      | 0.012             | 0.153            | 0.153      |

| SC+                                | PI   | 0.029      | 0.029             | 0.311            | 0.311      |

| STATCOM                            | FFPI | 0.004      | 0.004             | 0.132            | 0.132      |

| SVC+                               | PI   | 0.036      | 0.036             | 0.326            | 0.326      |

| STATCOM                            | FFPI | 0.011      | 0.011             | 0.151            | 0.151      |

**Table VII:** Inverter 1 and 2 DC power recovery time during AC and DC disturbances occur on the inverter 1 side.

| DC power recovery time for various |      | Inverter   | 1DC fault  | Inverter 1 side 3Ф A fault |            |

|------------------------------------|------|------------|------------|----------------------------|------------|

| RPC's in seconds                   |      | Inverter 1 | Inverter 2 | Inverter 1                 | Inverter 2 |

| SC                                 | PI   | 0.349      | 0.349      | 0.554                      | 0.554      |

| SC                                 | FFPI | 0.164      | 0.164      | 0.171                      | 0.171      |

| SVC                                | PI   | 0.361      | 0.361      | 0.566                      | 0.566      |

| SVC                                | FFPI | 0.171      | 0.171      | 0.178                      | 0.178      |

| STATCOM                            | PI   | 0.336      | 0.336      | 0.541                      | 0.541      |

| STATCOM                            | FFPI | 0.156      | 0.156      | 0.169                      | 0.169      |

| SC+SVC                             | PI   | 0.334      | 0.334      | 0.543                      | 0.543      |

| SC+SVC                             | FFPI | 0.155      | 0.155      | 0.170                      | 0.170      |

| SC+                                | PI   | 0.315      | 0.315      | 0.520                      | 0.520      |

| STATCOM                            | FFPI | 0.134      | 0.134      | 0.157                      | 0.157      |

| SVC+                               | PI   | 0.331      | 0.331      | 0.540                      | 0.540      |

| STATCOM                            | FFPI | 0.153      | 0.153      | 0.168                      | 0.168      |

**Table VIII:** Inverter 1 and 2 DC power recovery time during AC and DC disturbances occur on the inverter 1 side.

| DC power recovery |      | Inverter 1 side 2Φ AC fault |            | Inverter 1 side 1Ф AC fault |            |

|-------------------|------|-----------------------------|------------|-----------------------------|------------|

| time for various  |      |                             | 1          |                             |            |

| RPC's in seconds  |      | Inverter 1                  | Inverter 2 | Inverter 1                  | Inverter 2 |

| SC                | PI   | 0.543                       | 0.543      | 0.532                       | 0.532      |

| SC                | FFPI | 0.168                       | 0.168      | 0.164                       | 0.164      |

| SVC               | PI   | 0.554                       | 0.554      | 0.543                       | 0.543      |

| SVC               | FFPI | 0.173                       | 0.173      | 0.167                       | 0.167      |

| STATCOM           | PI   | 0.532                       | 0.532      | 0.521                       | 0.521      |

| STATCOM           | FFPI | 0.160                       | 0.160      | 0.154                       | 0.154      |

| SC+SVC            | PI   | 0.532                       | 0.532      | 0.520                       | 0.520      |

| SC+SVC            | FFPI | 0.164                       | 0.164      | 0.158                       | 0.158      |

| SC+               | PI   | 0.510                       | 0.510      | 0.498                       | 0.498      |

| STATCOM           | FFPI | 0.143                       | 0.143      | 0.141                       | 0.141      |

| SVC+              | PI   | 0.529                       | 0.529      | 0.518                       | 0.518      |

| STATCOM           | FFPI | 0.162                       | 0.162      | 0.156                       | 0.156      |

From the inverter side RMS AC voltage waveforms shown in Fig. 7, 8 and the results listed in table III, IV, the occurrence of TOV with the presence of a conventional PI controller for various RPC's can be understood. The hybrid RPC's (SC+SVC, SC+STATCOM and SVC+STATCOM) has improved TOV controlling capability, than their individual performance (SC, SVC, and STATCOM). In particular, SC+STATCOM have very less TOV among the various RPC's. The TOV values

further reduced due to the application firefly algorithm based PI controller compared to conventional PI controller.

# **4.3** Fault Recovery

The time taken by the HVDC system to recover the 80% of the pre-fault power after the fault clearance is known as DC power recovery time. The DC power recovery time is often desired the recovery ability of a DC system PI controller and the capability of the RPC's during system disturbances. From the inverter DC power recovery simulation results (Fig. 9-12 and Table V-VIII), it is observed that in all the cases during rectifier side AC system faults, the system recovery with the firefly algorithm based PI controller is slightly faster than the conventional PI controller. On the other hand, for the faults in the rectifier DC side and inverter AC and DC side, the hybrid RPC's (SC+SVC, SC+STATCOM and SVC+STATCOM) has reduced fault clearing time than their individual performance (SC, SVC, and STATCOM). In particular, the combination of SC and STATCOM is taking very lesser time to clear the fault among the various RPC's. Further, the firefly algorithm based PI controller makes the system recovery much faster than the conventional PI controller.

### 5. Conclusion

In this paper, performance investigation of hybrid RPC's in a multi-terminal HVDC system feeding weak AC networks was carried out in detail with firefly algorithm based optimal PI controller for rectifiers and inverters control. The different hybrid RPC's analyzed were SC+SVC, SC+STATCOM and SVC+STATCOM. This involvement can be very useful for designing and safeguarding persons, for analyzing the interaction between AC networks and HVDC systems under different operating environment. The HVDC transmission system model was developed in the Matlab environment. The transient performances of the hybrid RPC's in an HVDC system were compared with SC, SVC, STATCOM, under different fault condition to study the suppression of TOV and fault recovery. The simulation results validate that the equal mix of SC + STATCOM has the steady and fastest response and display the superiority of firefly algorithm based PI controller over the conventional fixed gain PI controller. The harmonic analysis result also assures the quality of power supply on the inverters AC side.

### 6. Acknowledgment

The authors gratefully acknowledge the support and facilities provided by the authorities of the Annamalai University, Annamalainagar, Tamilnadu, India to carry out this research work.

# 7. References

[1] S. Rüberg, A. L'Abbate, G. Fulli, A. Purvins, "Advanced Technologies for Future Transmission Grids-High-Voltage Direct-Current Transmission", Power Systems, Springer London, 2013, pp. 157-213.

- [2] J. Reeve, "Multiterminal HVDC Power Systems", IEEE Transaction on Power Apparatus and Systems, vol. 99(2),1980, pp. 729–37.

- [3] T. Sakurai, K. Goto, S. Irokawa, K. Imai, T. Sakai, "A New Control Method for Multi-terminal HVDC Transmission without Fast Communication Systems", IEEE Transaction on Power Apparatus and Systems, vol. 102, 1983, pp. 1140–1150.

- [4] A. Egea-Alvarez, J. Beerten, D. V. Hertem, O. G. Bellmunt, "Hierarchical power control of Multi-terminal HVDC grids", Electric Power Systems Research, vol. 121, 2015, pp. 207-215.

- [5] Vijay K. Sood, "HVDC and FACTS Controllers, Applications of Static Converters in Power Systems", Kluwer Academic Publishers, Boston, MA, 2004.

- [6] A. Gavrilovic, "AC/DC System Strength as Indicated by Short Circuit Ratios", IEEE International Conference on AC-DC Power Transmission, 1991,pp. 27-32.

- [7] S. Rao, EHV-AC HVDC Transmission and Distribution Engineering, Khanna publishers, New Delhi, India. 2003.

- [8] L. A. S. Pilotto, M. Szechtman, A. E. Hammad, "Transient AC Voltage Related Phenomena for HVDC Schemes Connected to Weak AC Systems", IEEE Transactions on Power Delivery, vol. 7(3), 1992, pp. 1396-1404.

- [9] A. V. Thio, J. B. Davies, "New Synchronous Compensators For The Nelson River HVDC System Planning Requirements and Specification", IEEE Transactions on Power Delivery, vol. 6(2), 1991, pp. 922-928.

- [10] Chan-Ki Kim, Gilsoo Jang, Byung-Mo Yang, "Dynamic performance of HVDC system according to exciter characteristics of synchronous compensator in a weak AC system", Electric Power Systems Research, vol. 63(3), 2002, pp. 203-211.

- [11] S. K. Tso, S. P. Cheung, "Fast Prediction of Transient Stability Margin in Systems with SVC Control and HVDC Link", IEEE International Conference on Energy Management and Power Delivery, vol. 2, 1995, pp. 456-461.

- [12] Chan-Ki Kim, Jin-Young Kim, Sung-Doo Lee, Eung-Bo Sim, "Stability Enhancement in HVDC System with STATCOM", Engineering, vol. 3(11), 2011, pp. 1072-1081.

- [13] M. Khatir, S. A. Zidi, M. K. Fellah, S. Hadjeri, M. Flitti, "The Impact Study of a STATCOM on Commutation Failures in an HVDC Inverter Feeding a Weak AC System", Journal of electrical engineering, vol. 63(2), 2012, pp. 95–102.

- [14] S. Nyati, S. R. Atmuri, D. Gordon, D. V. Koschik, R. M. Mathur, "Comparison of Voltage Control Devices at HVDC Converter Stations Connected to Weak AC Systems", IEEE Transactions on Power Delivery, vol. 3(3), 1988, pp. 684-693.

- [15] O. B. Nayak, A. M. Gole, "Dynamic Performance of Static and Synchronous Compensators at an HVDC Inverter Bus in a Very Weak AC System", IEEE Transactions on Power Delivery, vol. 9(3), 1994, pp. 1350-1358.

- [16] Y. Zhuang, R. W. Menzies, "Dynamic Performance of a STATCON at the HVDC Inverter Feeding a Very Weak AC System", IEEE Transactions on Power Delivery, vol. 11(2), 1996, pp. 958-964.

- [17] S. Seenivasan, S. Singaravelu, "Performance Investigation of a Monopolar HVDC Transmission System Feeding a Weak AC Network", International Journal of Engineering Inventions, vol. 4(5), 2014, pp.1-10.

- [18] A. Routray, P. K. Dash, Sanjeev. K. Panda, "A Fuzzy Self-Tuning PI Controller for HVDC Links", IEEE Transactions on Power Electronics, vol. 11(5), 1996, pp. 699-679.

- [19] P. K. Dash, A. Routary, S. Mishra, "A Neural Network based Feedback Linearising Controller for HVDC Links", Electrical Power Systems Research, vol. 50(2), 1999, pp. 125-132.

- [20] N. Bawane, A. G. Kothari, D. P Kothari, "ANFIS Based HVDC Control and Fault Identification of HVDC converter", HAIT Journal of Science and Engineering, vol. 2(5-6), 2005, pp. 673-689.

- [21] X. Zhou, C. Chen, Fan Yang, M. Chen, "Optimization Design of Proportional-Integral Controllers in High-voltage DC System Based on an Improved Particle Swarm Optimization Algorithm", Electric Power Components and Systems, vol. 37(1), 2009, pp. 78-90.

- [22] S. Seenivasan, S. Singaravelu, "Modelling and Simulation of Multi-terminal HVDC Transmission System Feeding Strong AC Networks with Firefly Algorithm based Optimal PI Controller", Global Journal of Pure and Applied Mathematics, Accepted for Publication, vol. 11, 2015.

- [23] X. S. Yang, Engineering Optimization: An Introduction to Metaheuristic Applications, Wiley, 2010.

- [24] X. S. Yang, "Firefly Algorithms for Multimodal Optimization", Stochastic Algorithms: Foundations and Applications- Springer Berlin Heidelberg, vol. 579, 2009, pp. 169-178.

- [25] X. S. Yang, X. He, "Firefly Algorithm: Recent Advances and Applications", International Journal of Swarm Intelligence, vol. 1, 2013, pp. 36-50.

- [26] Dufour, J. Mahseredjian, J. Belanger, "A Combined State-Space Nodal Method for the Simulation of Power System Transients", IEEE Transactions on Power Delivery, vol. 26(2), 2011, pp. 928-935.

### **Author Profile**

**S. Seenivasan** received Bachelor of Engineering in Electrical and Electronics in 2005 and Master of Engineering in Power System in 2011 from Annamalai University, Annamalainagar, Tamilnadu, India. He is currently pursuing Ph.D. degree in the Department of Electrical Engineering, Annamalai University. At present, he is an Assistant Professor in the Department of Electrical Engineering at

Annamalai University. His research interests are in high voltage DC transmission systems and soft computing techniques.

**S. Singaravelu** received Bachelor of Engineering in Electrical and Electronics in 1990, Master of Engineering in Power System in 1992 and Ph.D. in 2007 from Annamalai University, Annamalainagar, Tamilnadu, India. At Present, he is a Professor in the Department of Electrical Engineering at Annamalai University. His research interests are in power electronics, power systems, electrical

machines, wind/solar energy applications, high voltage DC transmission and smart grids.